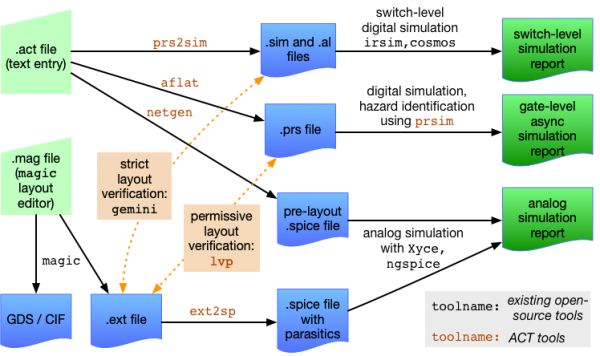

Custom Flow

The custom flow is for designing, simulating, and verifying hand-designed/optimized circuits.

In the standard custom circuit flow using ACT, there are two basic parts:

- Circuit design. This is done via text entry using an ACT file. In this file you can specify pull-up and pull-down networks as well as transistor sizes (width/length) and type (e.g. low threshold, high threshold).

- This circuit can be converted into a spice netlist using the

prs2nettool for analog simulation. This converts a hierarchical ACT design into a hierarchical spice netlist. - This circuit can be simulated using existing switch-level simulators like

irsimorcosmosusingprs2sim, which converts the hierarchical ACT design into a flat simulation file (.simand.al) that can be read byirsim/cosmos. - Asynchronous gate-level simulation can be done using the

prsimtool.

- Circuit layout. We assume that the layout is created using the

magicVLSI layout editor.- The circuit can be

:extracted from frommagicto create a.extfile. This contains the layout information and parasitics. - Magic also permits the creation of a simulation file using the built-in

ext2sim(an external tool in older versions, but a built-in command in version 8.x). This can be simulated usingirsim/cosmosas well. - The layout can be compared against the circuit design in two ways:

- The existing open-source

geminitool can be used for strict transistor-level comparison between the.simfile generated from the layout, and the.simfile created from the.actfile (prs2sim) - The ACT-provided

lvptool can be used to compare that the layout matches the production rules used to specify the logic. This tool does not check width/length of transistors, but rather checks that the gates are logically equivalent. It also requires all signals to be named consistently in the layout and ACT file.