This is an old revision of the document!

Generating spice netlist and simulation with Xyce

Files required:

- inv.act

- inv.sp

- test_inv.sp

- on_c5n.sp

(1) Input file with gate sizing

defproc inv (bool? i; bool! o)

{

prs {

i => o-

}

}

template<pint drive>

defproc szinv <: inv()

{

sizing {

o {-drive}

}

}

defproc INVX1 <: szinv<1> () { }

defproc INVX2 <: szinv<2> () { }

INVX1 A1;

INVX2 A2;

(2) Creating SPICE netlist from ACT file

Usage: prs2net [-dltBR] [-C <conf>] [-p <proc>] [-o <file>] <act> -C <conf> Configuration file name -c <cells> Cell file name -t Only emit top-level cell (no sub-cells) -p <proc> Emit process <proc> -o <file> Save result to <file> rather than stdout -d Emit parasitic source/drain diffusion area/perimeters with fets -B Turn of black-box mode. Assume empty act process is an externally specified file -l LVS netlist; ignore all load capacitances -S Enable shared long-channel devices in staticizers

$ prs2net -p "INVX1<>" -o inv.sp inv.act

* *---- act defproc: INVX1<> ----- * raw ports: i o * .subckt INVX1 i o *.PININFO i:I o:O *.POWER VDD Vdd *.POWER GND GND *.POWER NSUB GND *.POWER PSUB Vdd * * --- node flags --- * * o (combinational) * * --- end node flags --- * M0_ Vdd i o Vdd p W=3U L=0.6U M1_ GND i o GND n W=1.5U L=0.6U .ends *---- end of process: INVX1<> -----

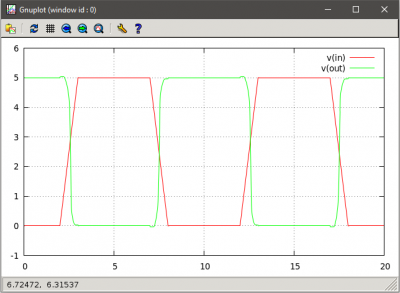

(3) Simulation with Xyce

* ************************************************** * Xyce simulation example * ************************************************** *** Default supply nodes *** .global vdd .global gnd *** Set Vdd to 5V, GND to 0V *** vd vdd 0 dc 5.0v vg gnd 0 dc 0.0v ** include nfet and pfet models *** .inc on_c5n.sp *** include circuit model *** .inc inv.sp *** set the voltage of "in" *** vp in 0 PULSE(0 5 2n 1n 1n 4n 10n) *** Instance of the inverter subcircuit *** X1 in out INVX1 *** Specify simulation and options *** .print tran format=gnuplot v(in) v(out) *** Run a transient simulation for 20 ns with 1ps timestep *** .tran 1p 20n .end

$ xyce inv_test.sp