## Welcome and Recap of Models

#### **Rajit Manohar**

Asynchronous VLSI and Architecture (AVLSI) Group Computer Systems Lab, Yale University

https://csl.yale.edu/~rajit/

https://avlsi.csl.yale.edu/act

Yale

### Abstractions for behavioral level modeling

- Message-passing programming in CHP

- Parallel collection of sequential programs

- Communication channels for information exchange

- Dataflow graphs

- Fine-grained parallel components

- Can be viewed as "simple subset of CHP"

- Easy to think about pipelines

- Communication channels for information exchange

- Links and joints

- Separation of state and actions

- Information exchanged via links

- Abstraction that captures common features of different ways to implement communication between two components

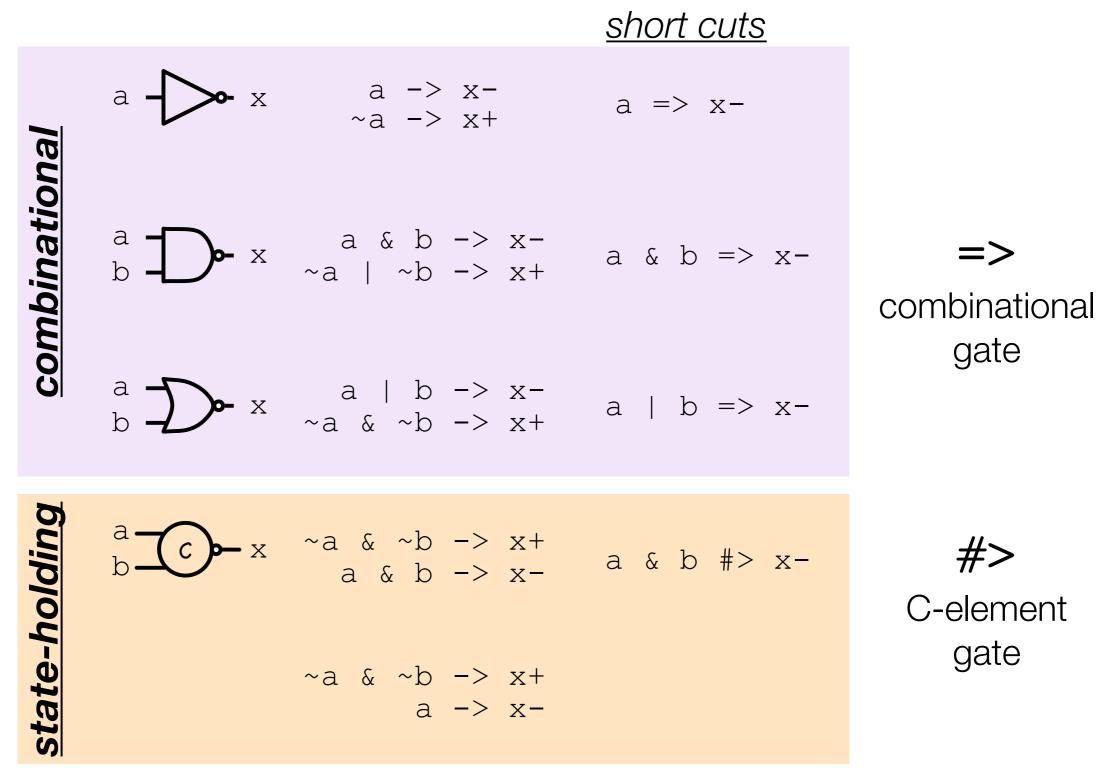

### **Gate-level modeling**

Digital logic

le

- All variables must be mapped into Booleans (0/1)

- If we already have a Boolean variable, direct mapping

- N-bit integers : use N one-bit variables

- Circuit often includes signal + complement

- Sometimes made *explicit* by having two variables for a Boolean

- Gates manipulate Boolean values

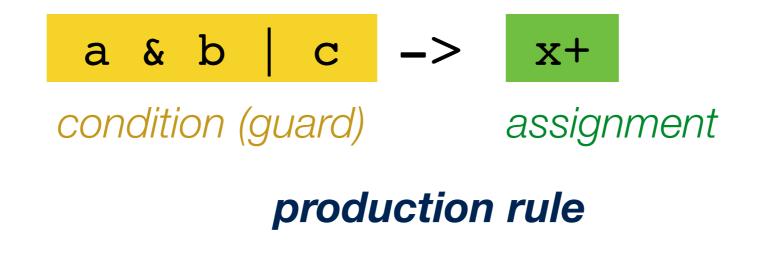

#### Syntax for gates in ACT

# Yale

AVLSI

## Going from channels to signals/Booleans

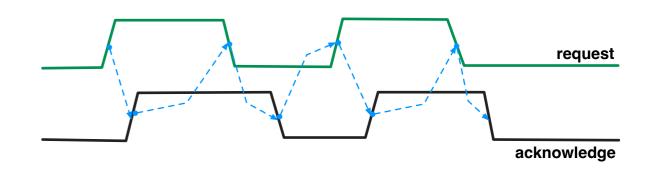

- Two parts of a channel

- Synchronization [blocking send and receive]

- Data transfer from sender to receiver

- Basic idea

ale

- Two signals : request and acknowledge

- One end asserts request

- Other end asserts acknowledge

- \* It is possible to have one signal

- One end asserts the signal

- The other end de-asserts the signal

- · Many variations of this idea in the literature

- We will describe some popular approaches today