# **ASIC** flow: mapping to cells

Rajit Manohar

Asynchronous VLSI and Architecture (AVLSI) Group Computer Systems Lab, Yale University

https://csl.yale.edu/~rajit/

https://avlsi.csl.yale.edu/act

#### Basic idea

- Convert entire design into a set of predefined blocks ("cells")

- Examples

- two-input NAND gate

- two-input C-element

- inverters with different sizing

- ... etc ...

- Each cell is implemented at the transistorlevel <u>once</u>

- Rectangular geometry with input/output connection points ("pins")

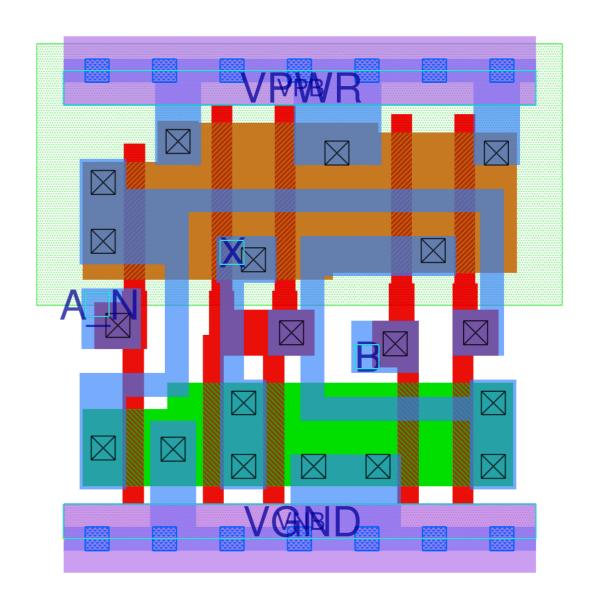

Example from Skywater 130 library for synchronous logic https://antmicro-skywater-pdk-docs.readthedocs.io

## Input: gate-level design in ACT

- Gate level design can have

- Explicitly instantiated cells

- Production rules

- Explicitly instantiated cells

- We use your cell instances as specified

- Each cell needs a physical implementation

- \* Example:

- ▶ Mapping arithmetic (e.g. "x + y") using logic synthesis results in a collection of gates selected by the logic synthesis tool

- \* A technology-independent cell library for combinational logic is available, based on James Stine's open-source library in 180nm ("OSU library")

# Input: gate-level design in ACT

Production rule mapping

Unique cells are identified

- ACT is re-written to explicitly instantiate these cells

- An ACT cell library is generated, consisting of <u>unique production rules</u> across the design

- An existing ACT cell library can be re-used, and is extended if necessary

#### Open-source ACT based on OSU library

```

export defcell NOR2X1 (bool? A, B; bool! Y)

prs {

A | B => Y-

ACT cell

sizing \{ Y \{-1\} \}

.subckt NOR2X1 vdd B qnd Y A

M0 a 9 54# A vdd vdd pfet w=4u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

Original

M1 Y B a 9 54# vdd pfet w=4u l=0.2u

OSU cell

+ ad=0p pd=0u as=0p ps=0u

M2 Y A gnd Gnd nfet w=1u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M3 gnd B Y Gnd nfet w=1u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

.ends NOR2X1

```

## Open-source ACT based on OSU library

```

.subckt HAX1 vdd qnd YC A B YS

M0 vdd A a 2 74# vdd pfet w=2u 1=0.2u

+ ad=0p pd=0u as=0p ps=0u

M1 a 2 74# B vdd vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M2 vdd a 2 74# YC vdd pfet w=2u 1=0.2u

+ ad=0p pd=0u as=0p ps=0u

M3 a 41 74# a 2 74# vdd vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M4 a 49 54# B a 41 74# vdd pfet w=4u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M5 vdd A a 49 54# vdd pfet w=4u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M6 YS a 41 74# vdd vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M7 a 9 6# A gnd Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M8 a 2 74# B a 9 6# Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M9 gnd a 2 74# YC Gnd nfet w=1u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M10 a 38 6# a 2 74# gnd Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M11 a 41 74# B a 38 6# Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M12 a 38 6# A a 41 74# Gnd nfet w=2u 1=0.2u

+ ad=0p pd=0u as=0p ps=0u

M13 YS a 41 74# gnd Gnd nfet w=1u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

.ends HAX1

```

Original

OSU cell

### Open-source ACT based on OSU library

```

export defcell HAX1 (bool? A, B; bool! YC, YS)

{

bool _YC, _YS;

prs {

A & B => _YC-

_YC => YC-

_YC & (A | B) => _YS-

_YS => YS-

}

sizing { _YC{-1}; YC{-1}; _YS{-1}; YS{-1} }

}

```

.subckt HAX1 vdd gnd YC A B YS

M0 vdd A a 2\_74# vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M1 a\_2\_74# B vdd vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M2 vdd a\_2\_74# YC vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M3 a\_41\_74# a\_2\_74# vdd vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M4 a\_49\_54# B a\_41\_74# vdd pfet w=4u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M5 vdd A a\_49\_54# vdd pfet w=4u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M5 Ydd A a\_49\_54# vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M6 YS a\_41\_74# vdd vdd pfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M7 a\_9\_6# A gnd Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M8 a\_2\_74# B a\_9\_6# Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M9 nd a\_2\_74# YC Gnd nfet w=1u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M10 a\_38\_6# a\_2\_74# qnd Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M11 a\_41\_74# B a\_38\_6# Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M11 a\_38\_6# A a\_41\_74# Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M12 a\_38\_6# A a\_41\_74# Gnd nfet w=2u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M13 YS a\_41\_74# qnd Gnd nfet w=1u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M13 YS a\_41\_74# qnd Gnd nfet w=1u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

M13 YS a\_41\_74# qnd Gnd nfet w=1u l=0.2u

+ ad=0p pd=0u as=0p ps=0u

### **Usage scenarios**

- "I have all my cells and they have been instantiated already!"

- \* ACT can use your cells as "black box" components

- \* For each cell, we will need

- ▶ Black-box: declare cell but do not provide a definition

```

export defcell MY_TWO_INPUT_CELL (bool? A, B; bool! Y);

```

- ▶ LEF, GDS, timing information from .lib (as in a normal cell library)

- Using an existing physical design flow? (e.g. a commercial tool)

- Map everything to cells

- Export Verilog netlist or DEF file

- Use your cell library

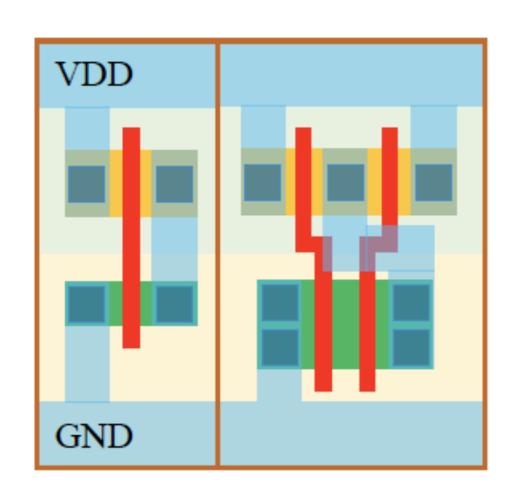

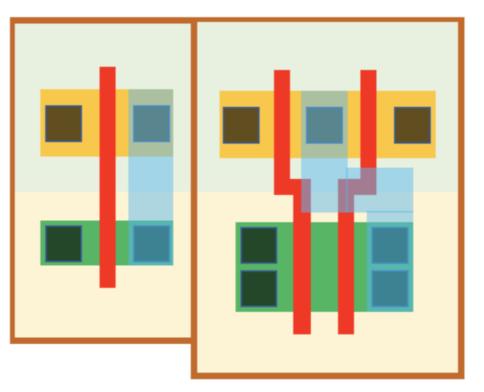

### **Usage scenarios**

- "I don't have any cells!"

- The ACT flow can get you started...

- ▶ Initial placement of transistors, ready to be wired up

- ▶ Key requirement: "Skyline" layout

- "I have some cells, but not sure if I have them all"

- \* ACT will let you know if there are any missing cells when mapping to the design

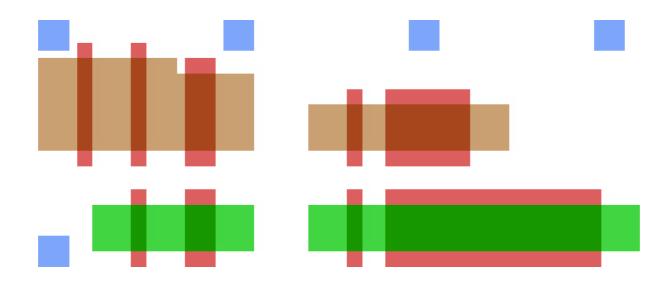

## ACT supports gridded cells

N-well

P-well

Cell outline

#### "Standard" cells

most cells are fixed height (e.g. 12 tracks), width is integer multiple of tracks; some "multi-height" cells

#### "Gridded" cells

cells width and height is integer multiple of tracks; can have "multi-deck" cells