## Yale engineering

# Gates and gate-level design

Rajit Manohar Computer Systems Lab Yale University

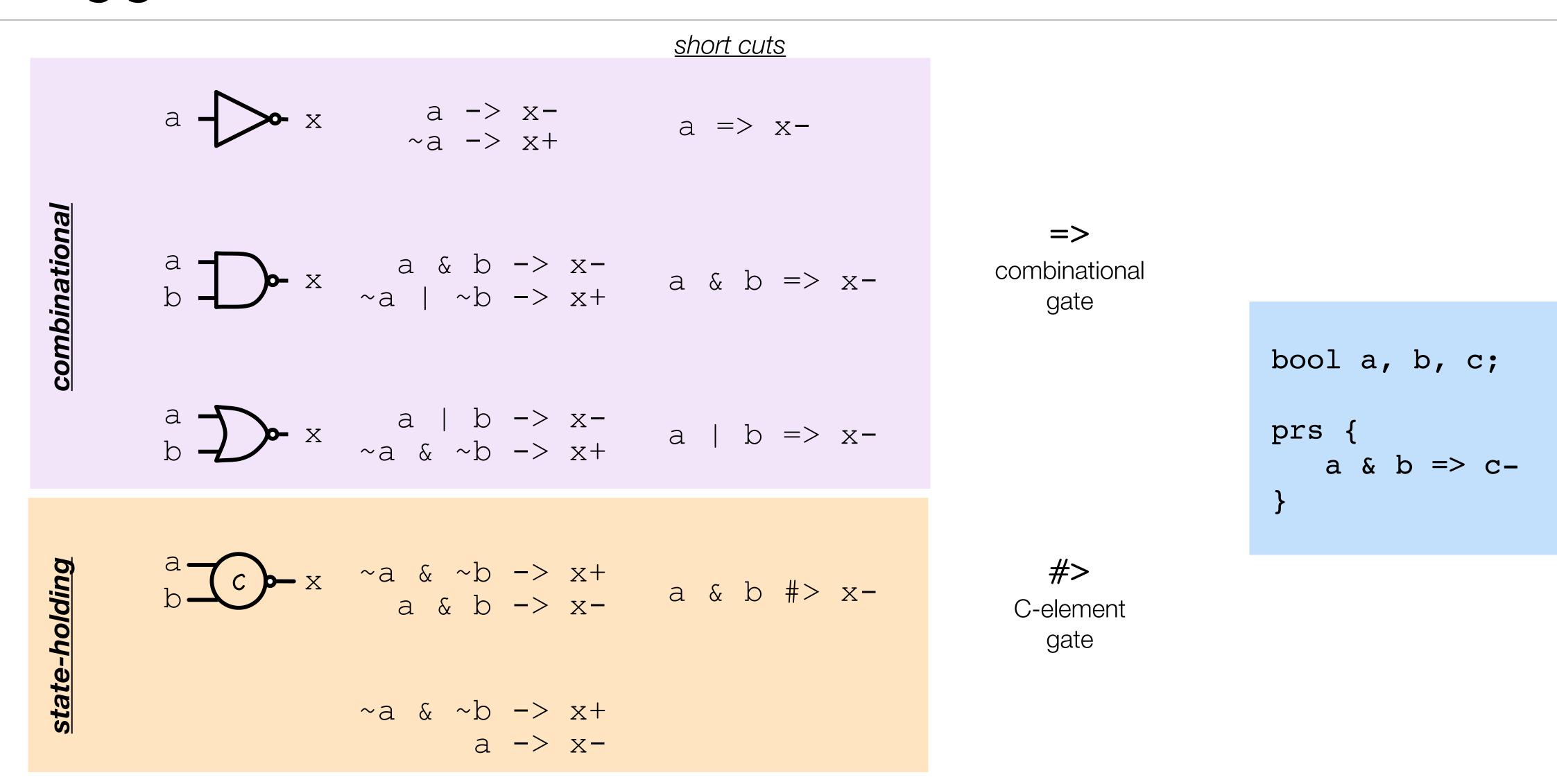

### **Gate-level modeling**

- Digital logic

- ✤ All variables must be mapped into Booleans (0/1)

- If we already have a Boolean variable, direct mapping

- N-bit integers : use N one-bit variables

- Circuit often includes signal + complement

- Sometimes made explicit by having two variables for a Boolean

- Gates manipulate Boolean values

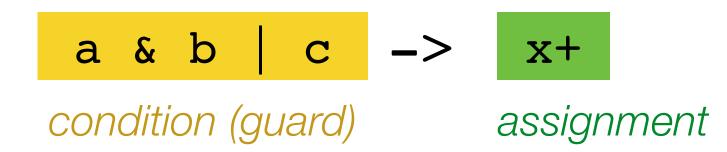

#### production rule

### Writing gates in ACT

Yale ENGINEERING

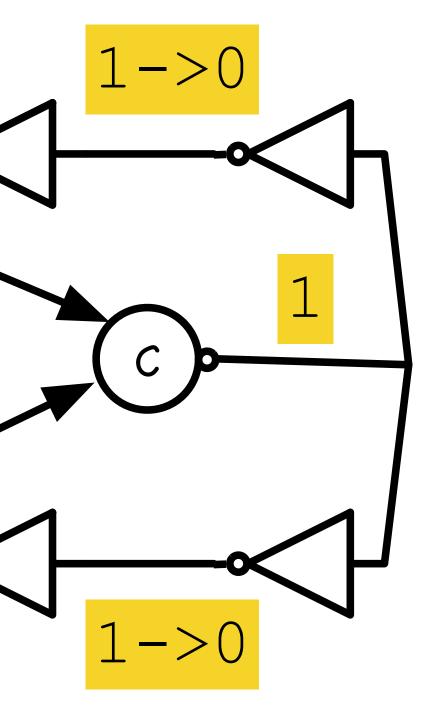

### A simple asynchronous circuit

• Two coupled oscillators

The C-element waits for the two inputs to agree

0