## ECE 4250/ENAS 8750 Introduction to VLSI System Design

### Rajit Manohar

Computer Systems Lab http://csl.yale.edu/~rajit

Fall 2025

Yale

**AVLSI**

ECE 4250/ENAS 8750: Digital VLSI

## What is ECE 4250?

"Computers in the future may weigh no more than 1.5 tons." — Popular Mechanics, 1949

"I think there is a world market for maybe five computers."

— Thomas Watson, Chairman of IBM, 1943

"I have traveled the length and breadth of the country and talked with the best people, and I can assure you that data processing is a fad that won't last out the year."

— editor in charge of Prentice Hall business books, 1957

... so what happened?

Yale

**AVLSI**

What is ECE 4250?

10<sup>7</sup>

10<sup>6</sup>

10<sup>5</sup>

10<sup>4</sup>

10<sup>3</sup>

10<sup>2</sup>

10

ECE 4250/ENAS 8750: Digital VLS

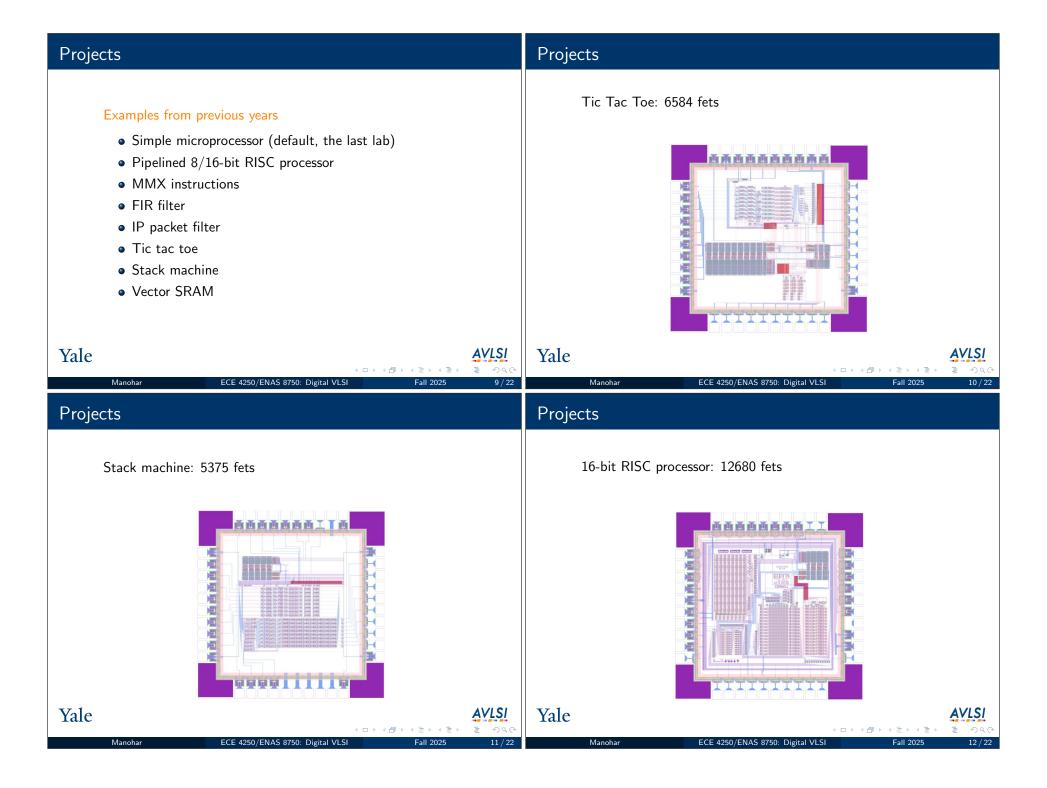

50 Years of Microprocessor Trend Data

**Transistors**

(thousands)

Single-Thread Performance (SpecINT x 10<sup>3</sup>)

Frequency (MHz)

Typical Power

Logical Cores

Number of

## What is ECE 4250?

The microelectronics revolution!

Number of components per Integrated

Moore, 1965

**AVLSI**

Yale

2000

Year Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batte

2020

1990

Yale

ECE 4250/ENAS 8750: Digital VLS

Manoha

1970

1980

2010

### Administrivia Administrivia Labs: • Lectures: 17 HLH 05, MW 11:35-12:50 You can do them on your laptop • WWW: Check announcements regularly! • Unix environment (Linux): an image will be provided with Grading: software pre-installed (additional pieces as needed) • All tools are written by my research group, or open source • 65% labs (5 labs: 5%+10%+15%+15%+20%) • 10% quizzes (9, every week, will drop lowest grade) Lab writeup: • 20% midterm • 5% instructor discretion • One page executive summary for each lab Electronic submission **AVLSI** Yale Yale **AVLSI** Manohar ECE 4250/ENAS 8750: Digital VLS Manohar Administrivia Administrivia Text: No required text. Late Policy: 0 (with the usual exceptions) For reference: Weste/Harris, CMOS VLSI Design If you contact me in advance, I can be flexible. Chip: Collaboration: • "Tape-in" this semester for all students. • Labs are in groups of two or three • "Tape-out" for students whose designs pass all final • General discussions among students permitted checks—hopefully everyone • Lab work is expected to be done separately • Test chip will arrive in the Spring. **AVLSI** Yale Yale **AVLSI**

Manohar

ECE 4250/ENAS 8750: Digital VLSI

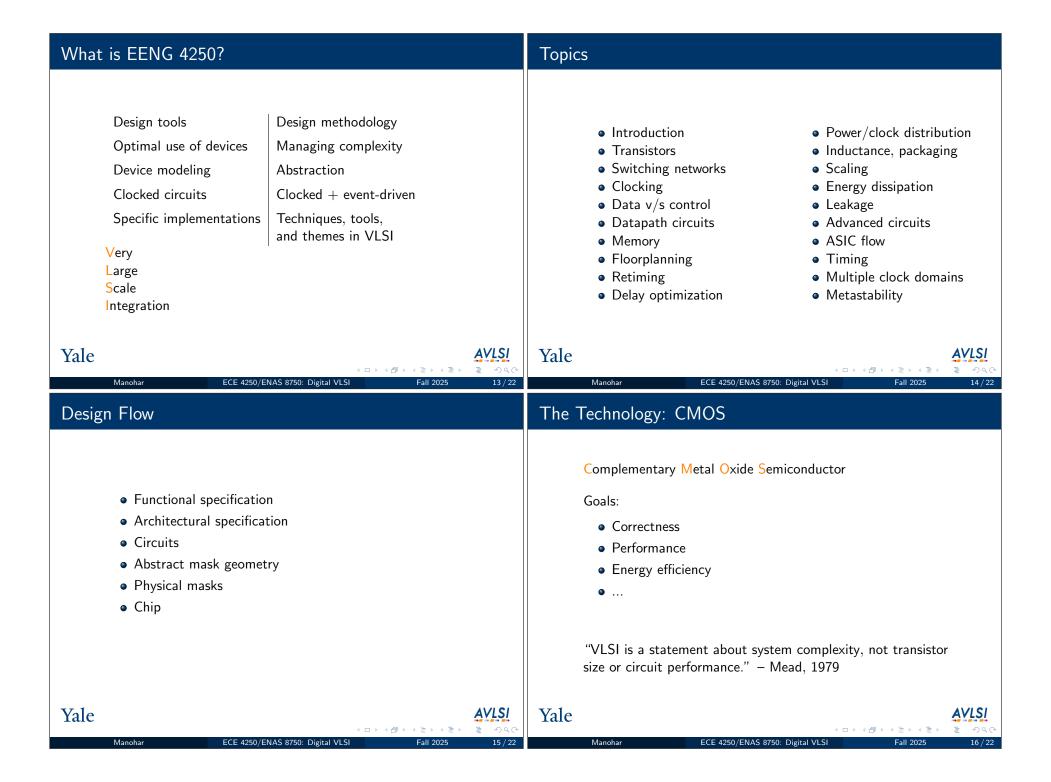

# Ideal scaling

Moore's law: # of transistors doubles every 18 months

Complexity analogy: Seitz and Mead, 1979. Imagine a city where streets are wires with 200m between blocks.

| Year | Spacing     | Chip size    | City                                          |

|------|-------------|--------------|-----------------------------------------------|

| 1963 | $50 \mu$ m  | 1mm          | town (4km)<br>county (100km)<br>state (100km) |

| 1975 | $10 \mu m$  | 5 <i>mm</i>  | county (100 <i>km</i> )                       |

| 1985 | $2\mu m$    | 10 <i>mm</i> | state (100 <i>km</i> )                        |

| 1995 | $0.5 \mu m$ | 20 <i>mm</i> | continent (8000km)                            |

Today:  $0.003 \mu m$  (3nm), 28 mm chip size!

## Yale

Manohar

# Ideal scaling

Key observation: abstraction!

#### Reuse:

• design tools, methods, circuits, abstract geometry

... as long as we understand how scaling works.

Mainstream modern CMOS process:

• Gate:  $0.005 \mu m (5nm)$

• Voltage: 0.8V

• FO1 inverter: < 1ps delay

Yale

Manohar ECE 4250/ENAS 8750: Digital VLSI

Fall 2025

!5 :