Low Power Embedded Systems

|

|

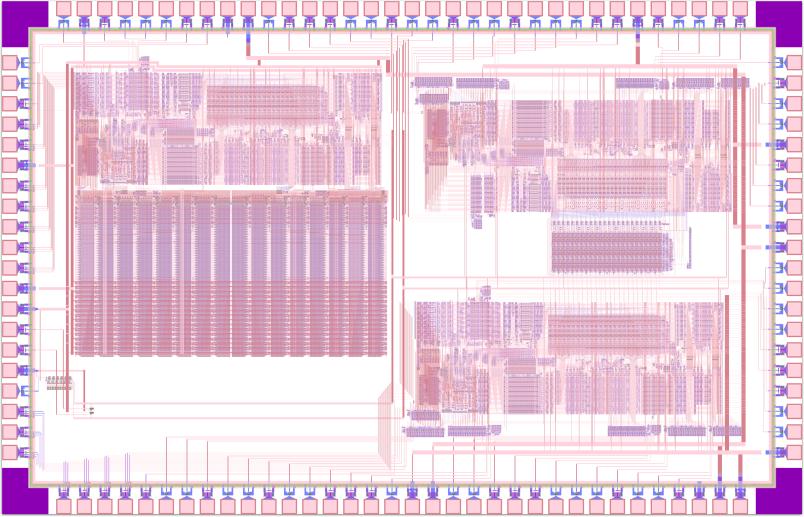

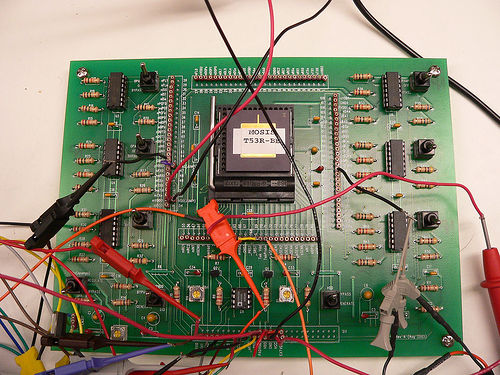

| First sensor network CPU |

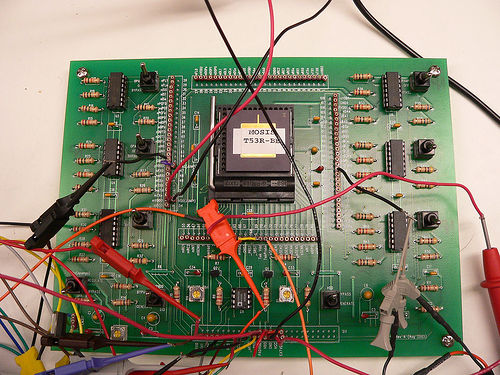

Bringup board |

|

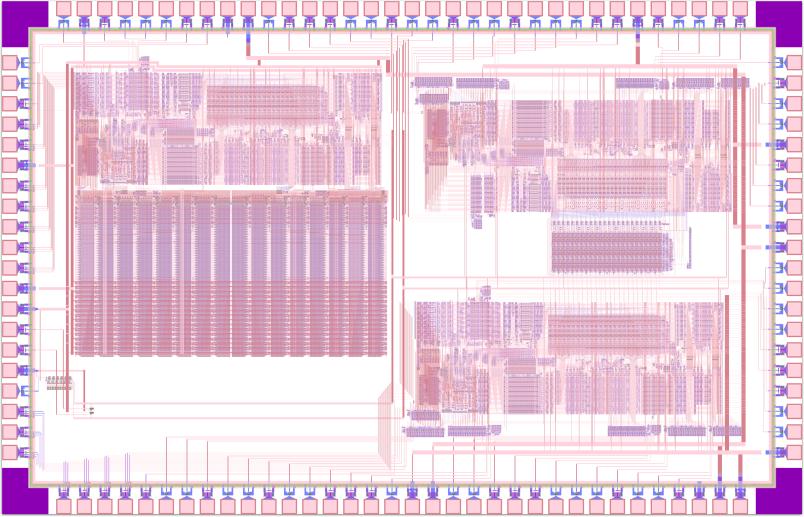

| ULSNAP chip as an Arduino shield |

We are investigating the use of asynchronous circuits to attain ultra

low power operation in the context of embedded systems.

For deeply

embedded applications, the goal is to design a completely self-contained

self-powered system. We collaborate with colleagues that have experitise

in MEMS and micro-battery design

so that the entire system is appropriately architected. For mobile

applications, the goal is to develop systems that have a lifetime that

is long enough so that users behave as if the mobile platform is always

available.

We have designed a processor that

uses an instruction set optimized for network protocol execution, and

which can be connected to an

RF data link to implement an efficient sensor node. The

net result is a highly efficient microprocessor optimized for sensor

network applications.

This is the first published design of a microprocessor optimized for

sensor networks.

We co-organized a workshop on

sensors and sensor networks at Cornell (June 2003).

- Collaborators

- Jaijeet Roychowdhury

- Participants

- Thomas Jagielski

- Siva Nalabothu

- Mattia Vezzolli

- Xiayuan Wen

- Alums

- Filipp Akopyan (Ph.D. 2011)

- Virantha Ekanayake (Ph.D. 2005)

- Clinton Kelly, IV (Ph.D. 2005)

- Carlos Tadeo Ortega Otero (Ph.D. 2014)

- Jonathan Tse (Ph.D. 2015)

- Publications

- Alex Huang, Amirmohammad Nazari, Robert Soulé, and Rajit Manohar.

An Energy Proportional High Speed Serial Link.

International Symposium on Asynchronous Circuits and Systems (ASYNC), June 2026.

(abstract)

- Gagan Deep Goru, Shreesha Sreedhara, Venkata Pavan Sumanth Sikhakollu, Thomas Jagielski, Rajit Manohar, and Jaijeet Roychowdhury.

DOIM140: A 140-spin, all-to-all connected, Oscillator Ising Machine IC in 180nm CMOS.

Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), April 2026.

(abstract)

- Venkata Pavan Sumanth Sikhakollu, Shreesha Sreedhara, Thomas Jagielski, Gagan Deep Goru, Jui-Hsin Hung, Rajit Manohar, and Jaijeet Roychowdhury.

DOIM50: A 50-Spin Fully Connected Oscillator Ising Machine IC for MU-MIMO Detection.

International Symposium on Nonlinear Theory and Its Applications, October 2025.

(abstract) — Best student paper nominee

- Abhishek Bhattacharjee, Quanquan C. Liu, Rajit Manohar, Raghavendra Pothukuchi, and Muhammed Ugur.

Dataflow-Specific Algorithms for Resource-Constrained Scheduling and Memory Design.

ACM Symposium on Parallelism in Algorithms and Architectures (SPAA), July 2025.

(abstract, pdf)

- Raghavendra Pothukuchi, Karthik Sriram, Michal Gerasimiuk, Muhammed Ugur, Rajit Manohar, Anurag Khandelwal, and Abhishek Bhattacharjee.

Distributed Brain-Computer Interfacing with a Networked Multi-Accelerator Architecture.

IEEE Micro (special issue on Top Picks from Computer Architecture conferences), 2024.

(abstract, pdf)

- Venkata Pavan Sumanth Sikhakollu, Shreesha Sreedhara, Rajit Manohar, Alan Mishchenko, and Jaijeet Roychowdhury.

High Quality Circuit-based 3-SAT Mappings for Oscillator Ising Machines.

International Conference on Unconventional Computation and Natural Computation, June 2024.

(abstract, pdf)

- Prafull Purohit, Johannes Leugering, and Rajit Manohar.

An Efficient Data Structure for Sparse Bit-Vectors with Applications in Neuromorphic Computing.

IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), July 2023.

(abstract, pdf)

- Karthik Sriram, Raghavendra Pothukuchi, Michal Gerasimuk, Muhammed Ugur, Oliver Ye Rajit Manohar Anurag Khandelwal, and Abhishek Bhattacharjee.

SCALO: An Accelerator-Rich Distributed System for Scalable Brain-Computer Interfacing .

IEEE/ACM International Symposium on Computer Architecture (ISCA), July 2023.

(abstract, pdf) — Best paper award — IEEE Micro Top Picks

- Abhishek Bhattacharjee, Rajit Manohar, and Karthik Sriram,.

RETROSPECTIVE: Hardware-software co-design for Brain-Computer Interfaces.

ISCA@50 Retrospective, June 2023.

(pdf) — ISCA-50 25-year retrospective

- Karthik Sriram, Ioannis Karageorgos, Xiayuan Wen, Jan Vesely, Nick Lindsay, Michael Wu, Lenny Kazan, Raghavendra Pothukuchi, Rajit Manohar, and Abhishek Bhattacharjee.

HALO: A Hardware-Software Co-Designed Processor for Brain-Computer Interfaces.

IEEE Micro, Vol. 43, Issue 3, Special issue from the HotChips 2022 conference, 2023.

(abstract, pdf)

- Prafull Purohit and Rajit Manohar.

Hierarchical Token Rings for Address-Event Encoding.

IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), September 2021.

(abstract, pdf)

- Karthik Sriram, Ioannis Karageorgos, Jan Vesely, Nick Lindsay, Xiayuan Wen, Michael Wu, Marc Powell, David Borton, Rajit Manohar, Abhishek Bhattacharjee.

Balancing Specialized Versus Flexible Computation in Brain-Computer Interfaces.

IEEE Micro (special issue on Top Picks from Computer Architecture conferences), 2021.

(pdf)

- Ioannis Karageorgos, Karthik Sriram, Jan Vesely, Michael Wu, Marc Powell, David Borton, Rajit Manohar, and Abhishek Bhattacharjee.

Hardware-software co-design for Brain-Computer Interfaces.

Proceedings of the IEEE/ACM Symposium on Computer Architecture (ISCA), June 2020.

(abstract, pdf) — IEEE Micro Top Picks

- Yu Chen, Xiaoyang Zhang, Yong Lian, Rajit Manohar, Yannis Tsividis.

A Continuous-Time Digital IIR Filter with Signal-Derived Timing and Fully Agile Power Consumption.

IEEE Journal of Solid-State Circuits, 53(2):418-430 (JSSC), February 2018.

(abstract, pdf)

- Yu Chen, Xiaoyang Zhang, Yong Lian, Rajit Manohar, and Yannis Tsividis.

A Continuous-Time Digital IIR Filter with Signal-Derived Timing.

2017 Symposium on VLSI Circuits, June 2017.

(abstract, pdf)

- Yu Chen, Rajit Manohar, and Yannis Tsividis.

Design of Tunable Delay Cells.

Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), May 2017.

(abstract, pdf)

- Carlos Tadeo Ortega Otero, Jonathan Tse, and Rajit Manohar.

AES Hardware-Software Co-Design in WSN.

IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2015.

(abstract, pdf)

- Benjamin Tang, Sunil Bhave, and Rajit Manohar.

Low Power Asynchronous VLSI with NEM Relays.

Proceedings of the 20th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2014.

(abstract, pdf) — Best paper nominee

- Jaeyeon Kihm, François Guimbretière, Julia Karl, Rajit Manohar.

Using Asymmetric Cores to Reduce Power Consumption for Interactive Devices with Bi-Stable Displays.

Proceedings of the ACM CHI Conference on Human Factors in Computing Systems (CHI), April 2014.

(abstract, pdf)

- Carlos Tadeo Ortega Otero, Jonathan Tse, Robert Karmazin, Benjamin Hill, Rajit Manohar.

ULSNAP: An Ultra-low Power Event-Driven Microcontroller for Sensor Network Nodes.

Proceedings of the IEEE International Symposium on Quality Electronic Design, March 2014.

(abstract, pdf)

- François Guimbretière, Shenwei Liu, Han Wang, Rajit Manohar.

An Asymmetric Dual-Processor Architecture for Low Power Information Appliances.

ACM Transactions on Embedded Computing Systems, 13(4), February 2014.

(abstract, pdf)

- Jonathan Tse, Benjamin Hill, and Rajit Manohar.

A Bit of Analysis on Self-Timed Single-Bit On-Chip Links.

Proceedings of the 19th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2013.

(abstract, pdf)

- Benjamin Tang, Stephen Longfield, Rajit Manohar, and Sunil Bhave.

Low Power ASIC GPS Tracking Loops: Quantifying the Trade-Offs Between Area, Power and Accuracy.

Proc. ION GNSS Technical Meeting, September 2012.

— Best presentation award

- Benjamin Tang, Stephen Longfield, Sunil Bhave, and Rajit Manohar.

A Low Power Asynchronous GPS Baseband Processor.

Proceedings of the 18th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2012.

(abstract, pdf)

- Carlos Tadeo Ortega Otero, Jonathan Tse, and Rajit Manohar.

Static Power Reduction Techniques for Asynchronous Circuits.

Proceedings of the 16th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2010.

(abstract, pdf)

- Filipp Akopyan, Rajit Manohar, and A. Apsel.

A level-crossing Flash Asynchronous Analog-to-Digital Converter.

Proceedings of the 12th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), March 2006.

(abstract, pdf) — Best paper award

- Yao-Win Hong, Birsen Sirkeci-Mergen, Anna Scaglione, and Rajit Manohar.

Dense Sensor Networks are also Energy-efficient: when `more' is `less'.

Proceedings of MILCOM 2005, October 2005.

(abstract, pdf) — IEEE Fred Ellersick Award for the best unclassified paper at MILCOM

- Virantha Ekanayake, Clinton Kelly IV, and Rajit Manohar.

An Ultra-low-power Processor for Sensor Networks.

Proceedings of the 11th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), October 2004.

(abstract, pdf, ps)

- Clinton Kelly IV, Virantha Ekanayake, and Rajit Manohar.

SNAP: A Sensor Network Asynchronous Processor.

Proceedings of the 9th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), pp. 24--33, Vancouver, BC, May 2003.

(abstract, pdf, ps)

- Rajit Manohar and Anna Scaglione.

Power Optimal Routing in Wireless Networks.

IEEE International Conference on Communications, pp. 2979--2984, Anchorage, AK, May 2003.

(abstract, pdf)

|